在工业控制计算机及系统制造领域,实时、精确的时钟控制是保障系统稳定运行、实现高精度同步与协调的关键。RCC(Real-Time Clock Controller,实时时钟控制器)时钟控制系统在其中扮演着核心角色。本文将深入解析RCC时钟控制系统的组成,并对其时钟原程序进行技术分析。

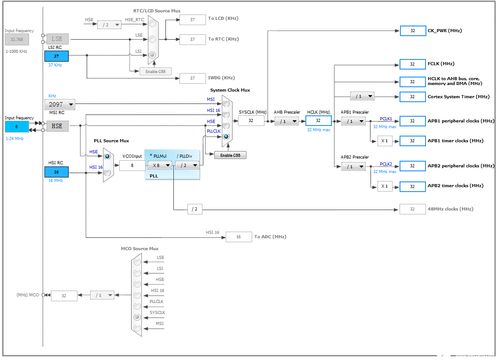

一、RCC时钟控制系统组成

RCC时钟控制系统是一个软硬件结合的精密体系,主要包含以下几个核心组成部分:

- 硬件基础:时钟源与振荡器

- 主时钟源:通常由外部高速晶体振荡器提供,作为系统主时钟的基准,频率通常在8MHz至25MHz之间,为CPU核心及高速外设提供时钟。

- 内部时钟源:包括内部高速RC振荡器和低速RC振荡器。前者作为主时钟源的备份或系统启动时的初始时钟;后者主要驱动独立看门狗和实时时钟模块,功耗极低。

- 锁相环:用于对原始时钟信号进行倍频或分频,生成系统所需的各种高频时钟信号,是提升系统运行速度的关键部件。

- 核心控制单元:RCC控制器

- 这是集成在工业控制计算机主控芯片(如基于ARM Cortex-M系列的MCU)内部的专用电路模块。它负责所有时钟源的开关、选择、分频/倍频配置,并将生成的时钟信号分配到系统的各个总线(如AHB、APB1、APB2)及外设(如GPIO、定时器、串口、ADC等)。

- 时钟分配与使能网络

- 这是一个由多路选择器、分频器和门控电路构成的网络。它根据RCC控制器的配置,将处理后的时钟信号精确送达目标模块。每个外设通常都有一个独立的时钟使能位,允许软件独立控制其时钟通断,以实现精细的功耗管理。

- 实时时钟模块

- 一个独立的、由低速振荡器(外部32.768kHz晶振或内部低速RC)供电的计时单元。即使主系统断电,在备份电池的支持下,RTC也能持续运行,为工业系统提供精确的日历、时间戳和定时唤醒功能。

- 软件驱动与配置接口

- 由芯片厂商提供的固件库或硬件抽象层代码构成,为上层应用程序提供配置RCC的API函数。这是程序员与RCC硬件交互的主要桥梁。

二、时钟原程序分析(以典型ARM Cortex-M环境为例)

时钟原程序通常指系统启动阶段初始化时钟系统的底层代码(如SystemInit()函数),其核心目标是稳定、快速地建立整个系统运行的时钟树。分析其关键流程如下:

- 复位后状态:系统上电复位后,默认使用内部高速RC振荡器作为系统时钟,此时系统运行在较低频率(如8MHz),以确保最基本的启动操作。

- 使能外部时钟:程序首先使能外部高速晶体振荡器的硬件电路,并等待其起振稳定(通过检测相关标志位)。此过程包含延时等待,以确保时钟信号可靠。

- 配置锁相环:程序配置PLL的时钟来源(通常选择稳定的外部晶振)、倍频系数和分频系数,以计算出目标系统时钟频率(如72MHz、168MHz等)。然后使能PLL并等待其锁定。

- 切换系统时钟源:将系统时钟源从内部的RC振荡器切换到已锁定的PLL输出。至此,CPU及高速总线运行在设定的高性能频率上。

- 配置总线与外围时钟:根据应用需求,对AHB、APB1、APB2等总线进行预分频配置,并逐个使能将要使用的外设时钟。此步骤实现了时钟树的精细化管理,未使用的外设时钟被关闭以节省功耗。

- 实时时钟配置:如果需要,程序会初始化RTC模块,选择其时钟源(外部低速晶振精度更高),并配置日历和时间。

程序特点与工业考量:

稳健性:代码包含大量状态检查和超时处理,防止因时钟源失效导致系统死锁。

可配置性:通过宏定义或配置表,可以灵活适配不同频率的晶振和系统性能需求。

原子性:关键的时钟切换操作通常是原子的或受保护序列的,以避免切换过程中产生毛刺。

低功耗设计:时钟的使能/禁用逻辑是工业控制系统实现动态功耗管理的基础。

###

RCC时钟控制系统是工业控制计算机的“心跳”发生器。其硬件组成的精密性与软件原程序的可靠性,共同决定了整个工控系统的实时性、同步精度和能效水平。深入理解其组成与初始化流程,对于进行工控系统底层开发、性能优化以及故障诊断都具有重要意义。在工业4.0和智能制造背景下,对高精度时间同步(如IEEE 1588协议)的需求日益增长,这使得RCC时钟系统的设计与分析变得愈发关键。